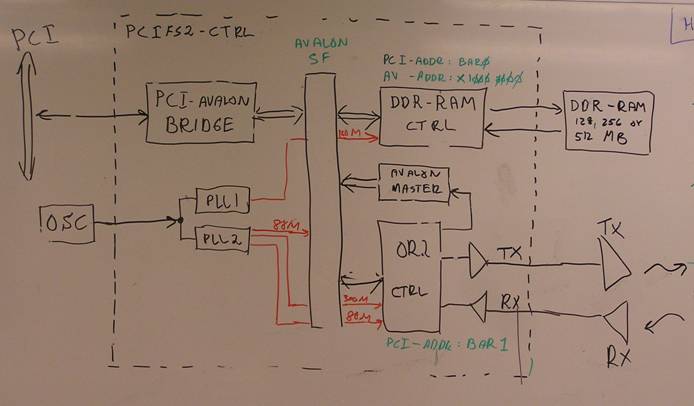

OptoRing

PC interface card.

As part

of the CCD3 camera system, the PCIFS2 card is the hardware tool making

it

possible for the host computer to communicate with the camera

controller as well

as grabbing the data transmitted in realtime from the controller. The

data-transport media is, as in the controller, the OptoRing. To ensure

that no

data is lost, no matter what the host computer is doing, a local memory

is used

as data buffer.

All the

necessary logic is placed in a FPGA ( Altera EP3C16 ), see figure.

Using

Altera’s SOPC concept, following building blocks are connected to an

Avalon

switch fabric:

·

PCI

to Avalon bridge. Altera ip

·

DDR-SDRAM

controller

Altera ip

·

OptoRing2

custom

module

Basic Board/FPGA

features

To

configure the EP3C16, an EPCS16 (16Mbit serial memory), an active

serial

interface, and a JTAG interface is available. This setup allows for the

addition

of a NIOS2 processor if that later becomes desirable. Local timing is

derived

from a 40MHz oscillator. All logic is interconnected by an Avalon

switch fabric

allowing several bus-masters to be active simultaneously. The Avalon is

running

120MHz.

Interfaces

to the PCI-bus and to the external fiberoptics is powered by the PCI

3.3V rail,

which also is the source for the local 1.2V FPGA core power-supply, the

2.5V

supply for the DDR-SDRAM and its interface and the DDR 1.25V active bus

termination. The fiberoptical parts itself are powered by the PCI

5V-rail. Thus

the board it both a 3.3V and 5V device.

Frame buffer

memory.

The board contains room for 4 DDR-DRAM chips distributed

in two banks. One ( Bank 0) or two banks can be populated. The chips

can be

either 64M x 8bit or 256M x 8bit ( TSOP66 package), allowing for a

capacity

ranging from 128 to 1024 Mbytes. This memory is intended to act as a

frame

store, ensuring that data is properly received independent of any other

activity in the PC.

Control registers.

The PCI to Avalon bridge is powering up as a 'simple

communication controller' during PCI

BIOS configuration. It will sign in as:

·

Device ID = 0x4F52 ( ASCII for 'OR' )

·

Vendor ID

=

0x1172 ( ALTERA id )

·

Function

078000 ( Simple

communication controller )

Use PCI-bios calls to get

access to the configuration data. Two BAR’s are assigned to the board:

·

BAR0 is the base address of the frame buffer memory

·

BAR1

is the base address of the OptoRing2 module ( se OptoRing

for register layout).